# ICL DAP (2)

# Customers as at 31 March 1990

# Totals:

# 74 systems

28 to universities

3 to government laboratories

43 to industry

# Breakdown:

Customer

**Application**

UK

# 20 to UK Universities/Research Centres

**Bristol University**

Edinburgh University(2)

Queen Mary College

Queen Mary College

Salford University

Southampton University

**Kent University**

Queen's University, Belfast

Strathclyde University

**SWURCC**

Exeter University Reading University

Cambridge University

Queen Mary College

Imperial Cancer Research Fund

Aberdeen University Manchester University

**London Hospital**

**Medical Research Council**

Molecular physics

Molecular biology, physics, neural net

Image processing, finite element

General Service

Engineer applications

Computer design simulation Parallel Processing Centre Parallel computing research

Signal processing Parallel computing

Fluid flow

Parallel computing Parallel computing

**DAP** training

Genetic sequence matching

Medical imaging Medical imaging Medical imaging

Genetic sequence matching

#### 2 to Government Laboratories

RAL

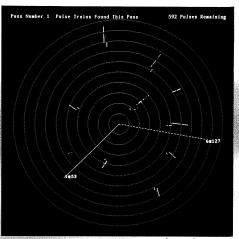

**RSRE**

Circuit simulation, image processing

Radar processing

# 5 to Industrial Companies

ICL

Plessey

BP

Hydraulics Research Ltd

A news agency

Defence applications

Radar processing

Image processing, neural networks

Fluid flow

Key word searching

Active Memory Technology Ltd 0734 661111 (voice) 0734 351395 (fax) 846931 (telex)

# USA

# 5 to USA Universities

Washington University

**Texas University**

RPI Rutgers

Old Dominion University

Image processing Signal processing

Image processing

Image processing Fluid dynamics

1 to Government Laboratory

**Argonne National Laboratory**

Parallel computing

34 to Industrial Companies

E-Systems

A defence contractor

Apple Computer Inc Texas Instruments

Severn Systems

US Army Corps of Engineers

NIST DoD

Lockheed

STX Systems

Ocean Research

NOSC

FCI

Radar processing, neural networks

Radar processing

Human interface research

Image processing

System Integration Image processing

Image processing

Signal processing

Image processing

Data compression Image processing

Simulation

Genetic sequence matching

# **EUROPE**

# 3 to European Universities

Erlangen University (Gr)

**Brussels University**

**Dublin University**

Parallel computing

CAD applications ECAD

3 to Industry

APTEC (Gr)

LERIS (Fr)

FTZ (Gr)

Distributor Distributor

Signal procesing

# **REST OF WORLD**

# 1 to Industry

Furukawa Electric Co Japan

Image processing

Active Memory Technology Ltd 0734 661111 (voice) 0734 351395 (fax) 846931 (telex)

# **DAPSERIES TECHNICAL OVERVIEW**

# Introducing the DAP/CP8 range

# INTRODUCTION

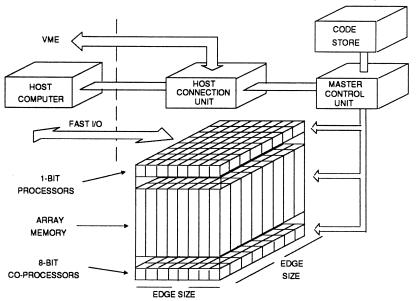

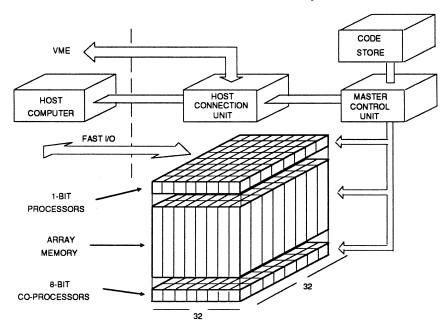

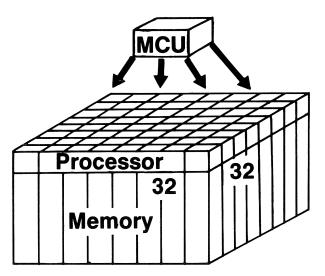

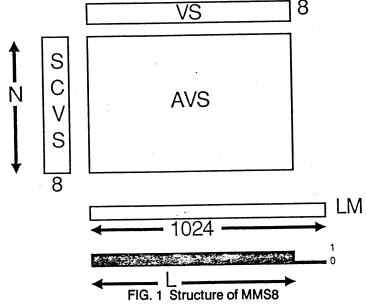

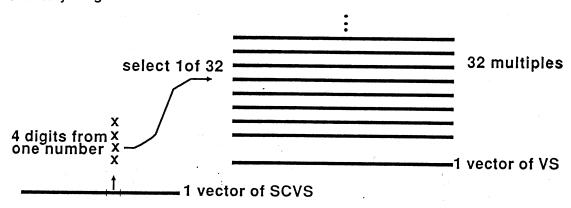

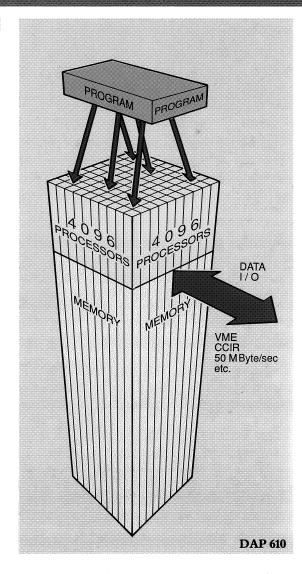

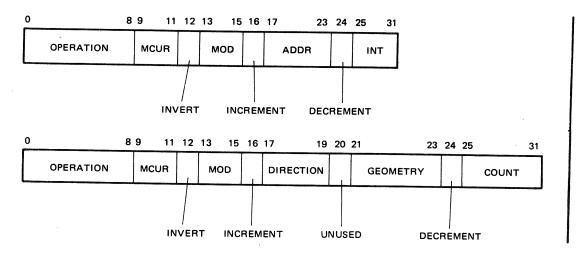

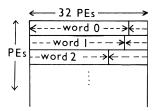

The DAP/CP8 range provides an arithmetic processing capability to work alongside the existing 1-bit processor elements (PEs) on computationally intensive tasks such as floating-point arithmetic and integer multiplication. Logically, each existing PE has a new co-processor associated with it, the two processors being able to work together by accessing the same set of array memory locations. The co-processors (or CP8) have 8-bit wide data paths, thus offering an order of magnitude performance increase over the original 1-bit PEs for suitable operations. Figure 1 shows the DAP/CP8 system with its array of 1-bit processors and array of 8-bit co-processors. The array edge size of the DAP/CP8 model 510C is 32, and for the model 610C is 64.

The new computation facilities can be regarded as an enhancement to the existing capability, and indeed it will be possible to upgrade existing systems, essentially by changing the array boards. The fact that the existing PEs are retained alongside the co-processors ensures compatibility with existing object code, and to take advantage of the co-processors it is necessary only to re-compile the user's Fortran-Plus programs.

Figure 1 Main components of the DAP/CP8 system. The array edge size is 32 for the model 510C and 64 for the model 610C.

Simple operations such as Boolean work or integer addition are already extremely fast and make full use of the array memory bandwidth. Thus there is no benefit in putting individual operations of this type into the co-processor. Likewise, all data communication other than the memory paths (ie neighbor operations, and row and column data paths) continue to be dealt with by the bit-organized processors. Of course this allocation of function is done automatically by the high-level language compilers, and therefore most users will be unaware of the existence of the co-processors, apart from noticing the higher performance.

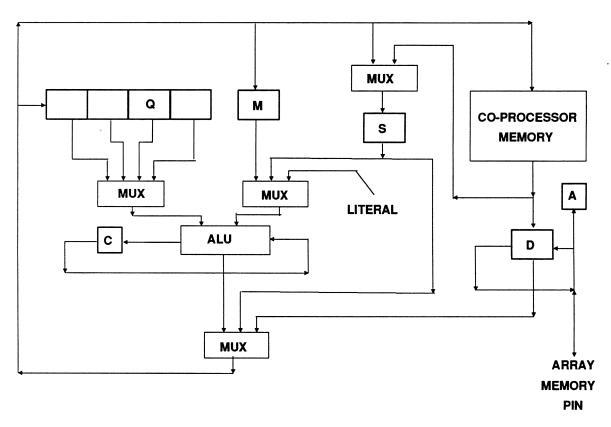

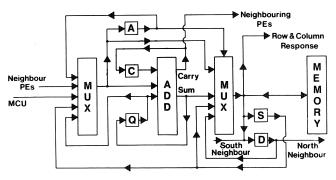

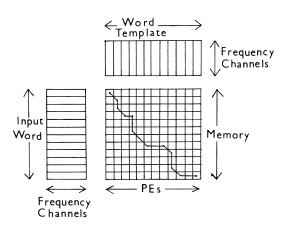

Figure 2 Relationship of the co-processor to the 1-bit PE and array memory.

Figure 2 shows one of the existing PEs and its associated section of array memory, with the 1-bit wide data path connecting them. Each bit-organized PE has a co-processor associated with it and a 1-bit connection to the memory path. Thus, either of the two processors can access or operate on data in the array memory, although there is no direct transfer of data between the two processors. Internal to each co-processor there is a memory of 32 bytes accessed 8 bits wide used for holding operands and workspace for one or two arithmetic operations at normal precisions. Thus the low-level sequence of operations to apply an intrinsic to one DAP-sized array is:

- copy the operand data from the array memory to the co-processor;

- perform the operation in the co-processor memory;

- copy the results back to the array memory.

This is analogous to the operation of the existing software intrinsics, where the operations are performed from array memory to array memory, but in that case a specific region of array memory is designated as a workspace for the intrinsic.

# CO-PROCESSOR FUNCTIONS

Although it has been designed with the multiply operation and floating-point work in mind, the co-processor, like the existing 1-bit PEs, offers great flexibility of function. Again there is flexibility of precision with a tradeoff between word length and performance, though in this case the natural step in word length is eight bits.

Figure 3 shows the main components of one co-processor, most of the registers and data paths being 8 bits wide. Although most of the register names are the same as those in the 1-bit PEs, and they have somewhat similar function, they are of course quite distinct from the registers in those PEs.

Figure 3 Main components of the 8-bit co-processor (CP8).

At the bottom right of the figure, the D register is used for interfacing to the array memory pin. For input of operands to the co-processor, successive array memory bits are shifted in until D holds a complete byte; that byte is then written to a location in the co-processor memory. For output of results, a byte is loaded into D from the co-processor memory, and then shifted one bit at a time with the data being output to the array memory pin. The single-bit 'A' register may be loaded from the array memory pin

and may be used for activity control in the array memory; the latter is implemented as a *read-merge-write* sequence on each array memory bit in turn.

Shifting of the D register for either input or output may take place concurrently with, and independent of, processing functions in the remainder of the co-processor; it is necessary to steal a cycle from the processing functions only for writing bytes from D to co-processor memory, or for loading D from that memory.

For processing functions, the co-processor memory is again written or read as one byte wide. In the latter case the result is always loaded into the S register, though S is also usable as a general-purpose register.

The Q register acts as an accumulator and is 32 bits wide. Any one of its four bytes may be selected for use as the left operand of the arithmetic-logic-unit (ALU). The complete Q register may be shifted right by one bit or one byte, and in the latter case the 8-bit value shifted in comes from the ALU via the multiplexer shown below it. Shifting of Q may be done unconditionally or may be dependent on a local condition.

The multiplexer shown below the ALU allows local selection of either the ALU output or the contents of the S register, thus giving a form of conditional control. As an implementation detail, this multiplexer is a convenient point to input the D register to the data path in order to write it to co-processor memory.

The M register acts as a general-purpose register and, as well as being able to load the complete register, it may be shifted one bit left or right. The least significant bit of M also has a special function in that it may control the multiplexer on the ALU output, or the shifting of Q.

A multiplexer on the right input of the ALU allows selection between the contents of the S register, the M register or an 8-bit literal value common to all the co-processors.

The ALU provides the usual addition and subtraction operations, and a variety of bit-by-bit Boolean functions. For the arithmetic operations, the carry out may be clocked into the single-bit C register, and used as a carry in for a subsequent instruction, thus allowing multiple byte arithmetic to be implemented.

Much of the performance improvement of the co-processor arises because of the wider data paths, but it is also significant that the Q register with its multiple bytes acts as a specialized form of memory, allowing both ALU operands to be supplied in a single cycle. The ability to shift Q conditionally is especially useful in operations such as floating-point alignment and normalization.

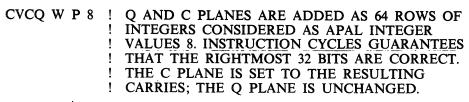

#### MICROCODE

Code for intrinsics to be run on the co-processors is written in a microcode language specific to the co-processor and, like the APAL language for the 1-bit PEs, offers great flexibility of function. At any given time, all the co-processors are executing the same micro-instruction sequence, so the co-processors may be thought of as a second SIMD array operating alongside the array of 1-bit PEs and communicating with it at high bandwidth via the array memory. Micro-instructions are held in a separate code store and issued by a sequencer which acts under the overall control of the master control unit (MCU). The microcode consists of many short sequences, each corresponding to an intrinsic function, or some other operation such as normalization checks. It is entered at the beginning of a specified microcode sequence which then runs to completion without branching; thus the micro-sequencer is extremely simple.

As a software convention, operands for any such intrinsic are initially in co-processor memory (rather than registers), and results, including exception flags where applicable, are returned to co-processor memory.

Microcode for common intrinsics is loaded at system load time and is shared between all user programs. There is also provision for microcode libraries or microcode specific to a particular application to be loaded along with individual applications programs.

Conceptually, the microcode memory and its associated controller are each a single entity common to the entire array. However, in order to allow co-processors to be added to existing systems with minimal effect on the rest of the system, the microcode is replicated on each array board. The individual micro-sequencers stay exactly in step with one another, although in principle they need not do so.

# CONTROL BY THE MCU

Overall control of the co-processors is provided by the MCU via new instructions compiled into the application program. These provide for the starting of the microcode controllers at a particular micro-instruction address, and for testing whether the co-processors are still busy. Other new instructions are provided to copy data between the co-processor D register and the array memory.

Once the MCU has started co-processor operation it is free to simultaneously perform other operations, including array memory accesses and issuing instructions to the bit-organized processors, until such time as it needs to access the results of the co-processor operation. The most likely case is that, while the co-processors are busy, the MCU will transfer into the co-processor memory the operands for the next intrinsic. Then, when the first intrinsic is finished, the second will be started; concurrently the results of the first intrinsic are copied to array memory and then the operands for the third intrinsic copied into the co-processor. By this means an efficient 'pipeline' is established making good use of both the processing capability and the memory bandwidth.

A common situation where pipelining is easy to organize from the software point of view is when a given intrinsic is applied to arbitrary-sized arrays that are larger than the DAP array dimensions, since in that case the same operation is applied to a succession of DAP-sized arrays. The potential for overlap may be exploited in other situations as the compiler technology is developed further.

### **BENEFITS**

The DAP/CP8 range offers a peak performance improvement of more than an order of magnitude over previous DAP systems for computationally intensive tasks. The Fortran-Plus compiler is well able to exploit this capability and offers outstanding ease of programming.

April 1990

Active Memory Technology Inc 16802 Aston Street, Suite 103 Irvine California 92714 U.S.A.

Tel (USA): (714) 261-8901 Fax (USA): (714) 261-8802 Active Memory Technology Ltd 65 Suttons Park Avenue Reading RG6 1AZ Berkshire United Kingdom

Tel (UK): 0734 661111 Fax (UK): 0734 351395

# The DAP/CP8 range: model 510C Massively Parallel Computing System

#### INTRODUCING THE DAP 510C

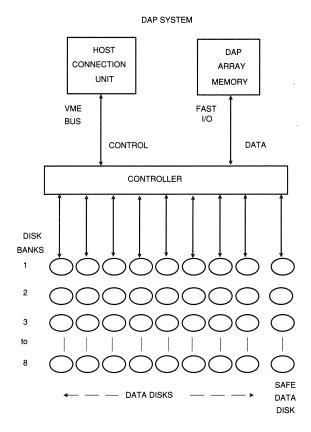

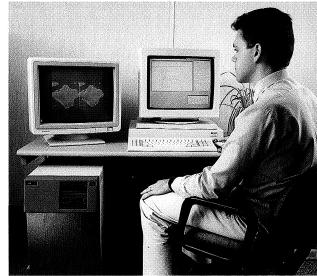

The DAP/CP8 range is a fine-grain, massively-parallel computing system designed and manufactured by Active Memory Technology. The DAP (Distributed Array of Processors) model 510C has an array of 1024 processor elements which work in parallel to achieve high-speed computing.

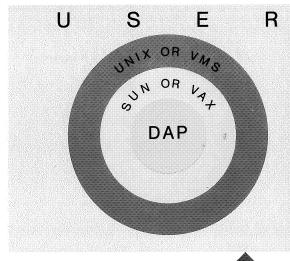

The DAP can be attached to computer systems, such as Sun<sup>1</sup> and VAX<sup>2</sup>, to gain speed improvements of up to several hundred times for many applications. The design of the DAP incorporates a high-speed input/output facility which can simultaneously transfer data at 40 Mbytes per second in each direction, with only a small effect on the processing speed. AMT provides a range of powerful software development tools and there are extensive software libraries to aid the rapid production of solutions for applications.

# DAP HARDWARE

The DAP 510C is a SIMD (Single Instruction, Multiple Datastream) machine in which 1024 processor elements simultaneously execute the

same instruction on data within their local memory. A technical description of the DAP is given in the AMT publication *DAP Series Technical Overview*.

The processor elements (PE) are arranged in a square array (32 x 32), each comprising a general-purpose bit-organized processor and an 8-bit wide co-processor (or CP8) for performing complex functions such as floating point arithmetic. Each PE has a local memory which ranges from 32 Kbits per PE (ie 4 Mbytes in total) up to a limit of 1 Mbits per PE set by the present architecture.

Each bit-organized processor is connected to its four nearest neighbors in the square array, and to row and column data paths used for rapid broadcast or combination of data. This processor also performs Boolean (logical) and arithmetic processing. However, computationally intensive tasks are generally done in the co-processor, which has 8-bit wide registers and data paths. Each co-processor has 32 bytes of storage for operands and intermediate results.

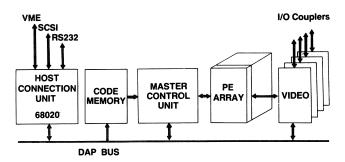

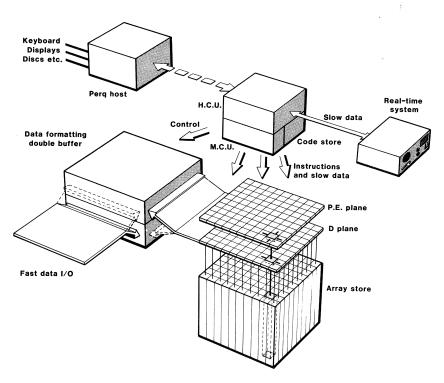

Program control is performed by a master control unit (MCU), which takes instructions from a code store, interprets them and controls the PEs, the memory and data transfers. The MCU also

Main components of the DAP 510C system.

- 1 Sun is a trademark of Sun Microsystems Inc.

- 2 VAX is a trademark of Digital Equipment Corporation

issues tasks to the co-processors, which execute in parallel a separate microcode instruction stream. A host connection unit (HCU) controls the interaction between the DAP and a host computer through a SCSI or VME bus interface. Also, the VME bus offers connection to other devices at up to 4 Mbytes per second.

High speed input and output is a major feature of DAP systems. The DAP 510C system requires only 3% of the processor cycles to sustain a transfer rate of 40 Mbytes per second. AMT supplies a number of fast I/O interfaces and peripheral sub-systems, including a high resolution video interface for viewing the data during processing, an I/O computer which can re-order the data during input and output, and a fast disk system. These products can be used to interface to other DAPs or to a variety of user-specified I/O devices.

The DAP 510C system is contained within a single cabinet that fits under a desk. The system requires standard 110 or 220 V power, is ambient air-cooled and needs no special environmental conditions.

DAP users will recognise the bit-organized processors in the DAP 510C as being identical to those in the current DAP 510 system. Existing DAP 510 systems can be easily upgraded, essentially by installing new array boards containing the additional co-processor chips.

# DAP SOFTWARE

All DAP systems are supported by a wide range of software:

- \* A high-level language called Fortran-Plus, which is an extended version of Fortran that allows the handling of matrices and vectors of any size, taking advantage of their intrinsic data parallelism.

- \* An assembly language called APAL, providing low-level control of the MCU and PE array if required.

- \* An interactive debugging system, which allows users to examine the state of the

- 3 UNIX is a trademark of AT & T Bell Laboratories

- 4 VMS is a trademark of Digital Equipment Corporation

- memory in terms of high-level program language variable names.

- \* A DAP run-time system supports host–DAP communications and access to fast I/O and VME devices.

- \* A general support library of mathematical functions, graphic support software and libraries for image and signal processing.

- \* A DAP simulator to allow those who do not have access to DAP hardware to develop and test DAP programs.

Program development takes place on Sun host systems under the UNIX<sup>3</sup> operating system, and on VAX hosts under VMS<sup>4</sup>.

# PERFORMANCE AND RELIABILITY

# **Performance**

Examples of the performance of the DAP 510C massively parallel system are:

- \* transfers between memory and processors at 1.3 Gbytes per second;

- \* Boolean (logical) operations at 10 billion per second;

- \* character handling at 1 billion per second;

- \* 8-bit integer multiply at 600 million per second

- \* 32-bit floating-point addition at 140 million per second.

# Reliability and Integrity

The DAP 510C is designed to be resilient and offers high reliability and easy maintenance. All data paths and memory in the system are parity checked. The complete array of PEs is duplicated, and all operations are checked by master/slave comparison, thus giving complete integrity – ensuring that all answers provided are 'correct.' The master control unit also validates the operations of its scalar computational units by master/slave comparison.

# Specifications of the DAP/CP8 model 510C

| OPERATIONS                                                                                              | INTERRUPTS                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data types Boolean, integer, character, floating point                                                  | MCU levels hardware fail, input/output subsystem,                                                                                                      |

| Precision                                                                                               | user program error, and HCU HCU communications                                                                                                         |

| Dimensions scalar vector (1 parallel dimension)                                                         | HOST CONNECTION UNIT (HCU)                                                                                                                             |

| matrix (2 parallel dimensions)                                                                          | Processor MC68020 system                                                                                                                               |

| INSTRUCTIONS                                                                                            | Memory 256 Kbyte PROM, 1 Mbyte dynamic RAM                                                                                                             |

| Address types row/column, word, bit-plane, register bit                                                 | Error handling memory parity check                                                                                                                     |

| Addressing facilities direct or modified, auto increment/decrement                                      | External interfaces:  SCSI port: to Sun systems, etc  VME bus: to VAX computers via DR11-W or DRB32                                                    |

| Addressing range - data 128 Mbytes                                                                      | interfaces, or to user-defined interfaces                                                                                                              |

| Addressing range – code 4 Mbytes                                                                        | Aptec IOC via Openbus<br>RS232 (two ports)                                                                                                             |

| MEMORY                                                                                                  | SPEED                                                                                                                                                  |

| Data memory                                                                                             | MCU and processor array 10 MHz clock                                                                                                                   |

| Program memory                                                                                          | Host Connection Unit                                                                                                                                   |

| Typestatic RAM                                                                                          | VIDEO INTERFACE (DAP-VO)                                                                                                                               |

| Error handling parity checks  Storage protection                                                        | Operation a high resolution graphic frame buffer                                                                                                       |

| MASTER CONTROL UNIT (MCU)                                                                               | Bandwidth up to 38 Mbytes per second                                                                                                                   |

| Functions scalar processor, array controller                                                            | Buffer                                                                                                                                                 |

| Registers                                                                                               | Video format                                                                                                                                           |

| Instruction sequencing program counter register, and hardware-controlled low-level loop                 | options; 60 Hz frame rate, non-interlaced, RGB, separate sync or sync-on-green                                                                         |

| Instruction control 4-stage pipeline                                                                    | Color display monitor                                                                                                                                  |

| Array control single instruction, multiple datastream (SIMD)                                            | Sony GDM1950 or equivalent  FAST I/O COMPUTER (DAP-IOC)                                                                                                |

| Error handling parity checks on data paths, master/slave checking on ALU components                     | Operation performs a comprehensive re-formatting of the input or output data in half duplex mode; two units can be connected for full duplex operation |

| PROCESSOR ARRAY                                                                                         | Bandwidth up to 40 Mbytes per second in each direction                                                                                                 |

| Number of PEs                                                                                           | Buffer 2 x 1 Mbyte buffer memories                                                                                                                     |

| and one co-processor                                                                                    | FAST DISK SYSTEM                                                                                                                                       |

| Bit-organized processor 1-bit wide data paths with accumulator, carry and activity registers            | Operation offers a high-speed transfer for bulk data applications                                                                                      |

| Co-processor 8-bit wide data paths and arithmetic unit,<br>32-bit wide accumulator, 32 bytes of storage | Bandwidth up to 16 Mbytes per second                                                                                                                   |

| Connectivityrow and column data paths,  4-way nearest neighbors                                         | Storage capacity up to 45 Gbytes                                                                                                                       |

| Error handling memory parity check,                                                                     |                                                                                                                                                        |

parity check on MCU data paths, master-slave checking on processor elements

# **PHYSICAL**

Dimensions ...... height 25.0 inches (63.5 cm), width 13.4 inches (34 cm), width at base 17.0 inches (43 cm) depth 31.0 inches (79 cm) Weight ...... 110 pounds (50 kg) Power ...... 110/220 VAC, 50/60 Hz, 750 Watts Cooling ..... internal fan

# **SOFTWARE**

Fortran-Plus compilation system General support library Digital signal processing library Image processing library Device driver configuration package APAL assembler **DAP** simulator

# **OEM PRODUCTS**

DAP systems are available as board sets for systems integrators.

**Active Memory Technology Inc** 16802 Aston Street, Suite 103 Irvine California 92714 U.S.A.

Tel (USA): (714) 261-8901 Fax (USA): (714) 261-8802 **Active Memory Technology Ltd** 65 Suttons Park Avenue Reading RG6 1AZ Berkshire United Kingdom

Tel (UK): 0734 661111 Fax (UK): 0734 351395 AMT is a multinational manufacturer of massively parallel computer systems with Company headquarters in Irvine, California. AMT maintains Research and Development activities at its Irvine, California location and at its European headquarters in Reading, U.K.

# Ferromagnetic Demonstration: Ising Model Simulation

# Introduction

The simulation of the ferromagnetic properties of materials is greatly enhanced by having powerful graphical interaction and high-speed computation. The Distributed Array of Processors (DAP) is ideally suited to such applications which for the present demonstration performs at about:

2 x CRAY X-MP 10 x CYBER 205 500 x FPS-264

The DAP's price/performance is also outstanding.

# Description

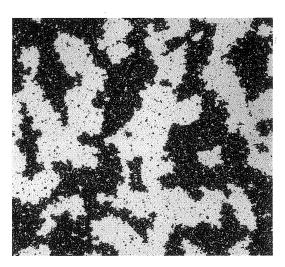

Ferromagnetic materials, such as iron, display magnetic properties below their critical temperature Tc. They spontaneously develop regions called 'domains' in which the elementary magnets (or spins) become aligned. The demonstration simulates the time evolution of a ferromagnet with the widely used Ising model on a  $1024 \times 1024$  lattice. The display shows each lattice point with red for positive and white for negative polarities.

As the temperature of the material is reduced below Tc, interesting patterns appear which evolve by random walks of the boundaries between domains of opposite magnetisation, with small domains tending to die out.

An external magnetic field will favour one of the two directions of magnetisation. If the field is applied at a time when the favoured direction (or phase) is in a minority, then bigger clusters of the favoured phase will tend to grow until the whole system is predominantly that phase; smaller clusters of the favoured phase will tend to die out. The critical cluster size and other properties of the domain dynamics depend on the values of the temperature and field, and how they vary with time.

# Fully Interactive

The DAP video output enables the state of the lattice to be directly viewed as the computation proceeds, with very little processing overhead. The main demonstration allows the temperature and field to be varied interactively using a 'mouse' attached to the host computer. The complete lattice is updated 20 times per second. The program can be slowed down in order to follow rapid changes.

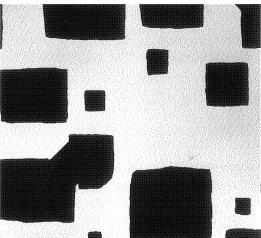

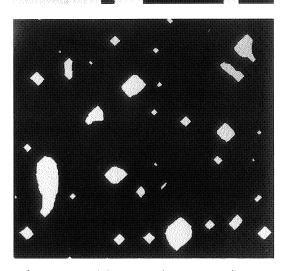

The variation of the domain shapes is illustrated in the pictures. At temperatures around Tc and at zero field, both fractal geometries and domains within domains are observed. Below Tc and with a magnetic field,

A ferromagnet just below its critical temperature. The top picture shows the appearance of magnetic domains when there is no external field. The two lower images show the appearance of square and diamond shapes when magnetic fields are applied.

expanding domains are observed as *square* shapes and contracting domains as *diamond* shapes, phenomena not directly observed before.

Computational physicists perform massive calculations using the Ising model; the DAP's combination of a fully interactive capability and the highest computational speeds adds a new dimension for both teaching and research.

# Algorithm and Codes

The lattice is represented by an array of logical variables. It is updated by each spin deciding whether to flip its magnetisation state according to a count of the states of its four neighbours and a probability table. The table is determined by energy considerations from the temperature and field values, and the selected probability is compared against a good quality 24-bit random number. The code uses the Monte Carlo method and runs at 20 million spin flips per second in the fully interactive mode.

Faster codes are available for zero field and for fixed temperatures. A subsidiary demonstration shows a much faster code for zero field that uses a cellular automata approach.

# Performance

The measured performance for the DAP 500 using various codes is compared below with recently published data on some other machines for *fixed temperature* and *zero field*.

| Code              | Machine   | Million spin flips/sec |          |

|-------------------|-----------|------------------------|----------|

| Monte Carlo       | DAP 500   | 105                    |          |

|                   | CYBER 205 | 38                     | (ref. 1) |

| Cellular automata | DAP 500   | 1250                   |          |

|                   | CRAY X-MP | 670                    | (ref. 2) |

|                   | CYBER 205 | 117                    | (ref. 3) |

|                   | FPS-264   | 2.2                    | (ref. 4) |

- 1. Wansleben S, Comp. Phys. Commun. 43 (1987) 315

- 2. Herrmann H J, J. Stat. Phys. 45 (1986) 145

- 3. Creutz M et al, Comp. Phys. Commun. 42 (1986) 191

- 4. Barkai D et al, John von Neumann Center, Princeton, Report JVNC 86-1 (1986)

# Benefits of using the DAP

DAP is the most cost-effective machine for this application, having the highest performance as well as being fully interactive. It is ideally suited to handling logical variables over large lattices.

This demonstration is based upon work done by the Physics Department of Edinburgh University and AMT consultants.

Active Memory Technology Ltd., 65 Suttons Park Avenue, Reading RG6 1AZ, United Kingdom.

Telex: 846931. Tel: 0734 661111. Fax: 0734 351395 Active Memory Technology Inc., 16802 Aston St., Suite 103,

Irvine, California 92714, U.S.A. Tel: (714) 261 8901. Fax: (714) 2618802

# DAP Video Interface - DAP-VO

# HIGH-RESOLUTION VIDEO INTERFACE

The DAP Video Interface – DAP-VO – is a high resolution graphic frame buffer which provides high speed transfer of data from the DAP massively-parallel computing system to a color display. This allows the user to view the data in the memory of the computer while the calculations are proceeding. Because of the

basic architecture of the DAP,

# HIGH-SPEED DATA TRANSFER

The AMT DAP (Distributed Array of Processors) system comes in two models:

|         | Number of  | Memory                |  |  |

|---------|------------|-----------------------|--|--|

|         | processors | bandwidth             |  |  |

| DAP 510 | 1024       | 1.3 Gbytes per second |  |  |

| DAP 610 | 4096       | 5.1 Gbytes per second |  |  |

The processor array has been specially integrated with a high-speed input/output facility (known as the D plane). A full description of the DAP system is contained in the AMT publication *DAP Series Technical Overview*.

To output data, the DAP-VO unit loads the contents of a memory plane into the D plane

in one DAP clock cycle (100 nanoseconds). This suspends the normal DAP instruction stream for one cycle only. The data in the D plane is then clocked out of the array at 10 MHz to give a sustained data transfer rate of 38 Mbytes per second, including all the overheads. The shifting out of the data is independent of the normal processing and therefore this transfer rate uses only 0.8% of the DAP 610 cycles, or 3% of the DAP 510 cycles.

# **HARDWARE**

The DAP-VO interface is a high-resolution video frame buffer, which provides real-time data visualization for both the DAP 510 and DAP 610 systems. The interface is available in two hardware configurations:

- DAP-VO-8, which contains two 8-bit image buffers with 8-bit to 24-bit look-up tables for displaying up to 256 colors selected from a total of 16 million. The size of each image buffer is 1 Mbyte.

- DAP-VO-24, which contains two 24-bit image buffers (8 bits each of red, green and blue) for directly displaying up to 16 million colors. Each image buffer is 3 Mbytes.

The double frame buffer configuration allows one frame to be displayed while a second is being updated with new data from the array. While the data transfer rate is the same for either board, the frame is three times faster for a VO-8 using 8-bit pixels than it is for a VO-24 using 24-bit pixels. The interface has red-green-blue and sync outputs which are used to feed a high-resolution monitor (see back page for specifications).

# SOFTWARE

A set of software associated with the video interface provides a straightforward and efficient means of using the data visualization facility of the DAP. Basic software is provided to construct images and cause them to be displayed on a high-resolution color monitor. The displayed image is  $1024 \times 1024$  pixels, each pixel being stored with a precision of up to 8 bits or 24 bits depending on the hardware option installed.

The software includes routines to draw dots, lines and characters in a data area in the user's program. This data area may be copied to the hardware frame buffer on a one-off or a regular basis. The software is optimized for the DAP architecture.

# Specifications

# DAP VIDEO INTERFACE

The video interfaces DAP-VO-8 and DAP-VO-24 are compatible with the DAP 510 and DAP 610 computer systems. These interfaces achieve a sustained data transfer rate of 38 Mbytes per second

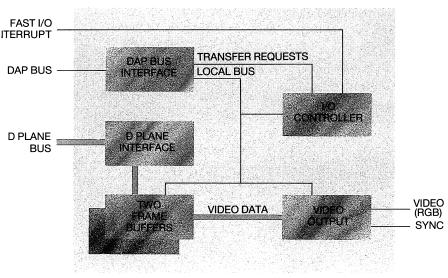

Functional block diagram of the high-resolution video interface.

# **IMAGE CHARACTERISTICS**

| DAP-VO-24                | DAP-VO-8                                                      |

|--------------------------|---------------------------------------------------------------|

| $\dots 1024 \times 1024$ | Dimensions $1024 \times 1024$                                 |

| from 1 to 24 bits        | Pixel format from 1 to 8 bits                                 |

|                          | Color generation<br>method translated<br>using look-up tables |

| up to 16 million         | Color range up to 256 (out of 16 million)                     |

| 2 × 3 Mbytes             | Frame buffer size 2 × 1 Mbyte                                 |

# VIDEO CHARACTERISTICS

| Display |    | 60 Hz frame rate, |  |

|---------|----|-------------------|--|

|         |    | non-interlaced    |  |

|         | RS | -343A compatible  |  |

Signal output ...... RGB analog, 0.7 volts peak-to-peak, BNC type connector, 75 ohm

sync: TTL, negative polarity either sync-on-green or separate sync

# **HORIZONTAL TIMING**

| 88 MHz (9.27 ns) |

|------------------|

| 6 KHz (15.61 μs) |

| 9.49 μs          |

| 1.33 μs          |

| 1.63 µs          |

| 3.15 μs          |

|                  |

# **VERTICAL TIMING**

| Frame rate  | 60.15 Hz (16.625 ms)     |

|-------------|--------------------------|

| Active time | 16.0 ms 1024 lines       |

| Front porch |                          |

| Sync pulse  |                          |

| Back porch  | $546.3 \mu s  35  lines$ |

Typical color monitors which conform to these specifications include the Hitachi CM2086A and Sony GDM1950 models.

Active Memory Technology Ltd 65 Suttons Park Avenue Reading RG6 1AZ Berkshire United Kingdom Tel (UK): 0734 661111 Fax (UK): 0734 351395

Active Memory Technology Inc 16802 Aston Street, Suite 103 Irvine California 92714 United States of America

Tel (USA): (714) 261-8901

Fax (USA): (714) 261-8802

AMT is a multinational manufacturer of massively parallel computer systems. Manufacturing and hardware R & D are conducted in the Irvine, California location. Software R & D activities are carried out at the company's facilities in Reading, UK.

# AMT DAP—a processor array in a workstation environment

# D.J. Hunt

The principle of single-instruction-stream multiple-datastream computing (SIMD) is embodied in the AMT DAP 500 and DAP 600 processor arrays, which have respectively 1024 or 4096 one-bit processors embedded in a memory module. The distributed array of processors (DAP) system has a memory bandwidth of up to 5.1 Gbyte/s. A standard Sun or VAX computer system acts as host to DAP, thus placing it in a workstation environment. A direct output from the DAP memory to a video monitor leads to the concept of 'data visualization'. Most applications programming is done in an extended FORTRAN language having matrices and vectors as basic elements as well as the usual scalars. The DAP architecture has been applied by more than 1000 users, and there is thus a wealth of expertise in applications and parallel algorithms that can be exploited.

Keywords: SIMD computing, DAP system, data utilization, FORTRAN, parallel algorithms

A number of themes provide the basis for the DAP 500 and DAP 600 systems:

- Parallelism through use of multiple function units is the key to ever increasing computational power.

- For a very wide class of applications, a single instruction—multiple data (SIMD) architecture is efficient in that only a single control unit is needed, and a regular grid interconnect gives a match to many problem data structures.

- Local memory associated with each processor gives high aggregate bandwidth, thus avoiding memory bottlenecks associated with scalar processors. In effect, the processing power is distributed throughout the memory.

Active Memory Technology Ltd, 65 Suttons Park Avenue, Reading, Berks. RG6 1AZ, UK

- VLSI technology is ideally suited to replication of functional units, thus giving a physically compact implementation.

- There is an increasing emphasis on the use of workstations, either alone or as an adjunct to some central computer system. Hence, DAP is configured as an attached processor, working in conjunction with such a workstation, or as a server on a network of workstations.

- 'Data visualization' via a high-resolution colour display is important in monitoring the progress of a computation, and in interpreting its results. Hence, a small fraction of the high-memory bandwidth of the DAP is made available for video output or other high-speed input-output operations.

#### **ARCHITECTURE**

The DAP 500<sup>1</sup> and DAP 600 are a new implementation, by Active Memory Technology, of the DAP concept previously researched by ICL<sup>2-4</sup>. DAP installations include the University of Edinburgh and Queen Mary College, London. The latter operate a DAP service, bringing the total number of users to over 1000 worldwide, and representing a wide variety of applications.

In providing processing power through a set of individual processors, a fundamental design issue is the complexity of the individual processors: for a given quantity of hardware, should there be a few powerful processors or a larger number of simple ones? DAP takes the extreme of the latter approach where the processors (known as processor elements, or PEs) are just one bit wide and there are very many of them: 1024 in DAP 500, or 4096 in DAP 600. Having very simple processors gives maximum flexibility in the higher level functions that can be programmed.

The memory data path is also one bit wide for each PE, and at 10 MHz clock rate this gives an overall

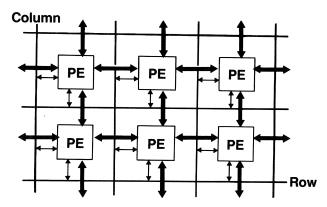

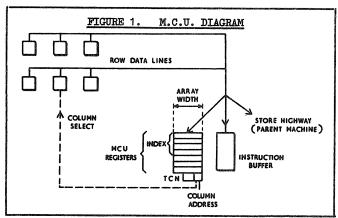

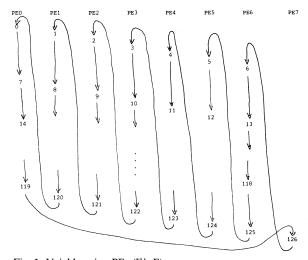

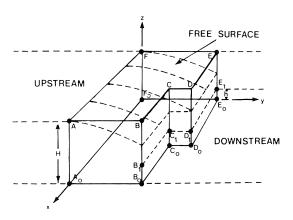

Figure 1. Principle of the DAP

memory bandwidth of 1.3 Gbyte/s for DAP 500 or 5.1 Gbyte/s for DAP 600. The logic of 64 processor elements (PEs) fits in a 176 pin semicustom chip, and the memory is provided using standard static memory components.

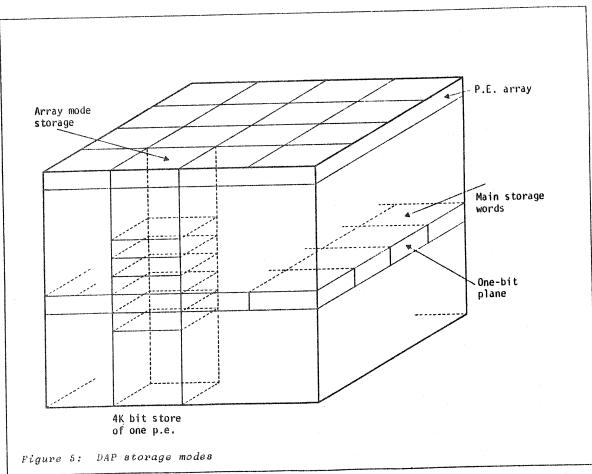

Figure 1 shows the basic principles of DAP operation. This shows a DAP 500, which has 1024 PEs arranged in a square array of  $32 \times 32$ , each with a one-bit wide memory below it, thus giving a cuboid of memory. The memory size is currently either 32 kbit or 64 kbit for each PE: a total of 4 Mbyte or 8 Mbyte for the whole array. DAP 600 has the same architecture, but has 4096 PEs arranged  $64 \times 64$ , and at least 16 Mbyte of memory.

Memory addresses are common to all PEs, so in a given instruction each PE accesses a bit of memory at the same memory address. Equivalently, a complete 'plane' of memory is being accessed at the same time. Generally, each data item is held in the memory of a particular processor, with successive bits of each data item occupying successively addressed locations. Thus a matrix of 16 bit values, for example, occupies 16 consecutive bit-planes of the memory. Some instructions, provide access to one row of memory (corresponding to one row of PEs), or one word of memory (32 consecutive bits in a row), selected from a memory plane.

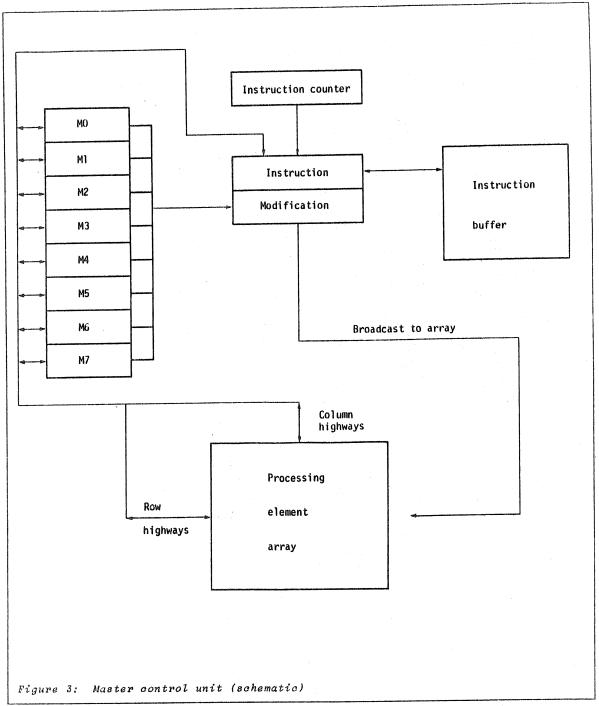

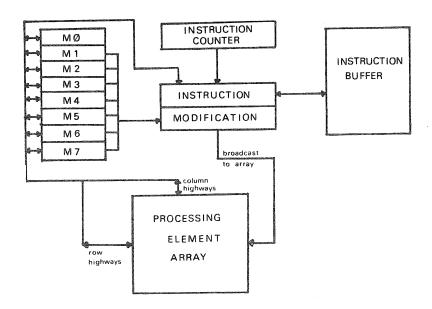

The instruction stream, common to all the PEs, is broadcast from a 'master control unit' (MCU). To be more precise, the MCU performs address generation and decoding on behalf of all the processors, and a set of decoded control signals is broadcast. This means that little decoding is needed in individual processors.

# **Processor element functions**

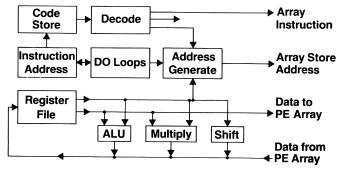

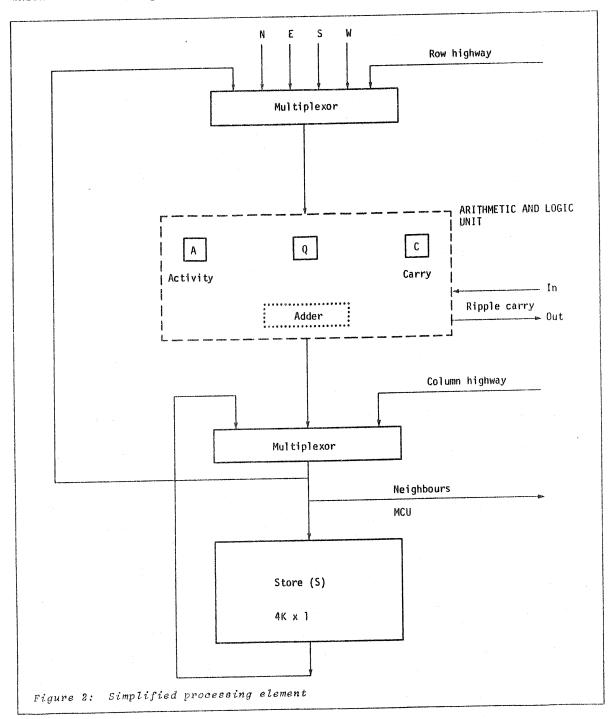

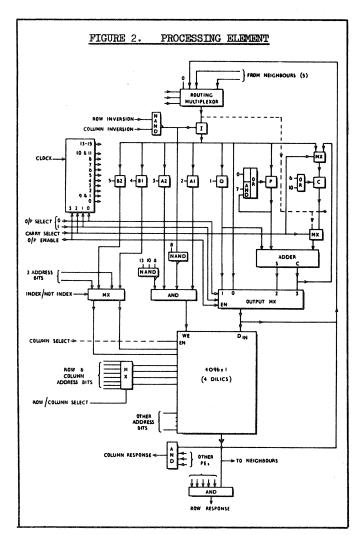

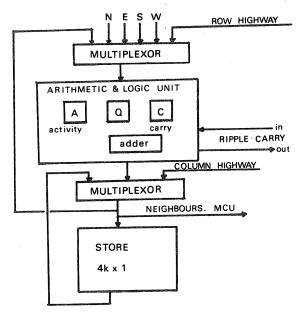

Figure 2 shows the main components of one PE and its connection to memory, each of the data paths and registers shown being just one bit wide. The main components of the PE are three one bit wide registers, named A, C and Q respectively, and an adder that

performs arithmetic and logic functions. The detailed usage of the registers depends on how the DAP is programmed, but the Q register generally serves as an accumulator, and the C register holds a carry.

In a typical PE operation, the input multiplexor (at the left side of the figure) selects an operand bit from memory which is then input to the adder along with values from the C and Q registers. These three inputs are added, producing a sum, which is optionally clocked into Q, and a carry, which is optionally clocked into C. An add operation on 16 bit integers, for example, is performed by 16 successive one bit adds starting at the least significant end, with the C register holding the carry between each bit position and the next.

The multiplexor near the right side of the figure selects data to be written back to the memory. In some cases, the A register acts as a control input to this multiplexor. This means that for a given instruction, in those PEs where the A register is *True* the sum output of the adder is written to memory, but in those where A is *False* the old memory contents are selected and rewritten. This activity control is equivalent to 'switching off' selected PEs in that the old memory contents are preserved, and is very important in implementing conditional operations both within functions and at the applications level.

An activity pattern may be loaded into the A register via the input multiplexor, and there are options to either write that value directly into A or to AND it with the existing A register contents. This latter option is very convenient for rapidly combining several conditions.

# Array interconnect

Although much processing is done with each PE working on data in its own local memory, it is important to be able to move data around the array in various ways, and two such mechanisms are provided.

The first interconnection mechanism is that each PE can communicate with its four nearest neighbours in the array. Inputs from these North, East, South and West neighbours are shown at the left of Figure 2. Since the PEs implement a common instruction stream, then if one PE is accessing its Northern neighbour, say, then so is every PE. The overall effect is that a plane of bits in the

Figure 2. A processor element

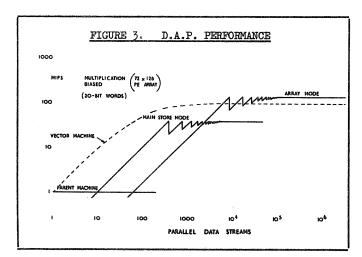

Figure 3. Connectivity

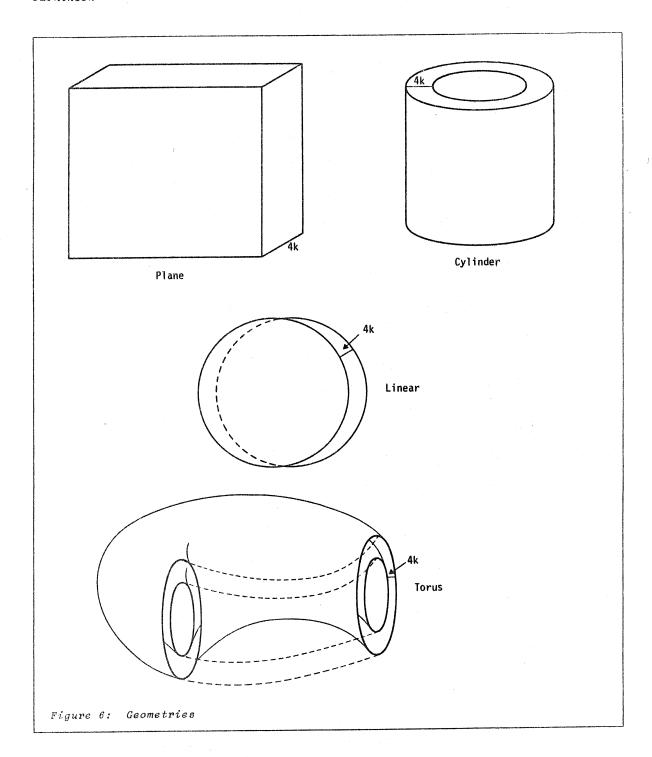

Q registers of the set of PEs may, in one clock cycle, be shifted one place in any of the four possible directions. A matrix of words may be shifted by shifting each bit plane of the matrix in turn, and longer distance shifts are implemented by successive shifts of one place. Such operations are important in applications such as the solution of field equations by relaxation.

The second array interconnection is two sets of data paths that pass along the rows of PEs and along the columns of PEs respectively. These paths are shown in Figure 3 for a small section of the array, along with the nearest neighbour connections mentioned above. One use of these data paths is in broadcasting a row of bits, such that each row of PEs receives the same data pattern, and similarly for broadcasting a column of bits. These broadcast operations each take just one basic clock cycle. Another use is in extracting data from the array, where the basic operations are to AND together all the rows or to AND together all the columns; variants of these operations permit data to be extracted from a single row or column.

Row and column data paths are important in areas such as matrix algebra. For example, in matrix inversion they are used to extract the pivot column of a matrix and replicate it in every column. Another case is a rapid global test implemented by ANDing all the rows in the array and then testing the result for all 1s.

# Master control unit

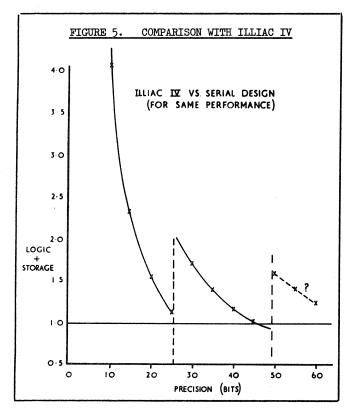

As already mentioned, the PE array is controlled by the master control unit (MCU). This is a 32 bit processor responsible for fetching and interpreting instructions, and its main components are shown in Figure 4. Instructions are held in a codestore (separate from the array data store) which holds 512 kbyte or 1 Mbyte, each instruction being 4 byte.

The MCU implements scalar functions including control transfers such as subroutine entry and exit, but most of the instructions are passed on to the array for execution. Hence, an important part of the instruction decode is to provide control signals for the PEs.

Array operations usually involve loops of a few

instructions, and the MCU provides explicit hardware support for these via a 'DO' instruction in the assembly language. Once such a loop is initiated, there are no overheads for loop control since this is dealt with by dedicated hardware. Another important aspect of these loops is the ability for instructions within the loop to automatically reference successive store addresses on successive passes of the loop, again without any execution time overhead.

The lower half of the figure is a conventional data path. The register file has dual port access, and the usual arithmetic, logical and shift operations may be performed upon the register contents. There are 14 general purpose registers, and one register dedicated for supervisor use.

Some of the array instructions involve broadcasting data to the array, and some receive data from the array; these paths connect to the MCU data paths as shown at the bottom right of the figure. The details depend on the array size:

- On DAP 600 the MCU data paths are 32 bit wide but the array paths are 64 bit wide. Logic known as the array support unit interconnects these data paths and provides a further 'edge register' of length 64 bits, which thus matches the array edge size. Complete edge-sized values (for example an array row) may be transferred between the array and the edge register, or words (32 bit items occupying half of a row or column) may be transferred between the array and an MCU register.

- On DAP 500 there is a direct match between the 32 bit data paths in the MCU and the 32 bit width of the row and column data paths in the array. Hence, no array support unit is needed, but the equivalent edge register functionality (32 bit wide) is provided using a spare location in the MCU register file.

# Fast input-output

In many applications, fast processing implies high data rates to or from external devices, and the DAP architecture provides this capability with only a small impact on processing performance. In the processor element diagram (Figure 2), the register shown as D may

Figure 4. Functions of the master control unit

Figure 5. DAP system organization

be loaded from the memory or written back to the memory, but does not otherwise take part in PE operations. Having loaded the plane of D registers from a plane of memory, the D plane may be shifted towards the North edge of the array, so that successive rows of the D plane are output at that edge. The D plane may similarly be used for input to the DAP by presenting successive data words as inputs at the Southern edge of the array. This shifting is done independently of the normal array instruction stream and is usually done at a faster clock rate.

The D plane is controlled by one of a number of input-output couplers, rather than by the instruction stream, so this I/O facility may be thought of as a fast DMA operation. For shifting the D plane, the coupler clocks the D plane independently of the array instruction stream. However, to load or store the D plane (which is, of course, necessary after each complete plane has been output or input), the coupler makes a request to the MCU along with the required memory address. This loading or storing suspends the normal instruction stream for one clock cycle.

Where a DAP system has more than one coupler installed, the couplers arbitrate amongst themselves for use of the D plane, so the available bandwidth is shared between them. Couplers include buffering, which both matches the D plane clock speed to the external interface and avoids any crisis times associated with D plane arbitration.

For the DAP 500, the D plane connection at the edge of the array is 32 bit wide, and the overall bandwidth is 50 Mbyte/s, while only using 4% of the available memory bandwidth. For the DAP 600, the D plane connection is potentially 64 bit wide, but in practice most couplers will have only 32 bit wide paths giving again 50 Mbyte/s, but using 1% of the memory bandwidth.

An important coupler already in use provides a video display facility. The patterns to be displayed are computed by the DAP in the array memory, then transferred to one of two frame buffers in the coupler for continuous refresh of a standard monitor via the usual colour lookup tables and digital-to-analogue converters. The screen resolution is  $1024 \times 1024$  pixels, each pixel being eight bits, or with an option for 24 bit.

Other couplers provide an external digital interface for input or output, either via a simple FIFO buffer, or via a more sophisticated double buffer arrangement with facilities for general purpose reordering of data as it passes through the coupler. External interfaces include a serial link (which may provide DAP-to-DAP connection, or links to other bus systems via a remote adaptor card), or high-density digital TV.

# System organization

Figure 5 shows how the various DAP components connect together. With the DAP 600, the array support unit, mentioned above, is added between the MCU and the array. During DAP processing there is a continuous flow of instructions from the code memory to the MCU and thence to the array. If I/O is in progress, then there is a concurrent flow of data between the D plane in the array and an I/O coupler.

The DAP bus along the bottom of the figure provides overall communication, including interfacing to a host computer system which provides program development facilities and access to conventional filestore and peripherals. A typical host is a Sun system running Unix\* (connected via a SCSI interface), or a VAX system running VMS\*\* (connected via a VME bus), the detail of the interfaces being managed by the HCU (host connection unit). DAP programs are downloaded into the code memory and array memory via the DAP bus, which also serves as a command interface to control entry to specified DAP subroutines. The RS232 interface shown in the figure is available for diagnostic purposes.

The HCU is built around a Motorola 68020 microprocessor system running the VRTX† real time kernel. It performs a supervisory function including the allocation of DAP memory to user programs. In the event of a hardware failure it also provides a diagnostic capability. The lowest level of control of DAP user programs resides in the MCU itself which runs a supervisor program in privileged mode to deal with scheduling of user programs and interrupt handling.

Control of the I/O couplers is done by privileged MCU code in response to a supervisor entry from a user program, the necessary sequence of commands being sent to the coupler via the DAP bus. When a transfer is in progress, the coupler also uses the DAP bus to request the MCU to perform D plane loading or storing; this is actioned automatically by the MCU hardware.

The VME bus may also be used to connect to medium speed peripherals, taking advantage of the wide range of standard boards available in that format. A transfer on such a device is again initiated by a supervisor call from a user program, but the MCU passes on the request to the HCU for detailed management of the transfer.

<sup>\*</sup> Unix is a trademark of Bell Telephone Laboratories

<sup>\*\*</sup> VAX and VMS are trademarks of Digital Equipment Corporation

<sup>†</sup> VRTX is a trademark of Hunter & Ready Inc.

#### **SOFTWARE**

#### FORTRAN Plus

The main programming language for DAP is known as FORTRAN Plus\*5—an extended version of FORTRAN 77 having matrices and vectors as basic elements as well as scalars. This language has been the main influence on the parallel processing facilities in the proposed ISO/ANSI standard, currently referred to as FORTRAN 8X.

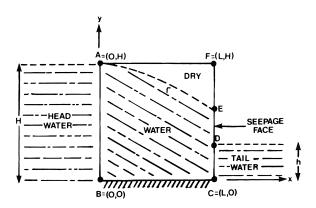

To illustrate some of the features of FORTRAN Plus, as well as parallel algorithm techniques, an example subroutine is given below. This performs a solution of Poisson's equation using an elementary relaxation techniqe; naturally the DAP has in practice been used with many more sophisticated algorithms.

```

SUBROUTINE SOLVE( FIELD , EPSILON)

REAL

FIELD( , )

REAL

EPSILON

4 C

REAL OLD(,), TEMP(,)

6

7

LOGICAL INSIDE( , )

8

INSIDE = ROWS( 2, 31 ) .AND. COLS( 2, 31 )

9

FIELD(INSIDE) = 0.0

10 C

11 100 CONTINUE

OLD = FIELD

12

TEMP = SHSP( FIELD ) + SHEP( FIELD )

13

14

FIELD( INSIDE ) = 0.25*

( TEMP + SHNP( SHWP( TEMP ) )

15

IF ( MAXV( ABS( FIELD - OLD ) ) .GT. EPSILON )

GOTO 100

16 C

RETURN

17

18

END

```

Subroutine SOLVE is callable from another FORTRAN Plus subroutine and takes two parameters: a real matrix FIELD which contains initially the boundary conditions and into which the solution is to be placed; and a real scalar EPSILON which is a measure of the final accuracy required. In FORTRAN Plus, an array declaration with the first subscript null signifies a vector whose length matches the DAP dimension, or in general a set of such vectors. In this case (lines 2, 5 and 6) the first two subscripts are null, meaning a matrix that matches the DAP in size.

Line 8 sets up a logical matrix to define the interior region; points where the matrix is False are fixed boundary points. In this example, intrinsic functions ROWS and COLS are used; ROWS(2,31) is a Boolean expression which is True in rows 2 to 31 inclusive and False elsewhere (rows 1 and 32 for DAP 500). Thus, a  $30 \times 30$  region of interior points is defined.

If this code was compiled to run on the DAP 600, the interior region would occupy only the top left quadrant of the processor array. However, changing the row and column numbers specified in line 8 would allow a problem with an interior region of up to  $62 \times 62$  points to be computed on the DAP 600. In general, any required boundary shape could be defined in line 8, and the rest of the code would be independent of that shape.

In line 9 the interior points are initialized. This is an assignment of a real scalar value to a matrix, the scalar being implicitly replicated to form a matrix-sized expression. Use of a Boolean matrix as a mask on the left of the assignment, in this case INSIDE, causes the assignment to be performed only where the mask is *True*. Thus the boundary values are preserved.

Line 12 saves the current field value in order to detect changes later; a single statement copies an entire matrix, element to corresponding element, all the copies being done in parallel.

Lines 13 and 14 perform the relaxation step. At each point the sum of the four neighbouring points in the North, East, South and West directions is needed. A shifted copy of a matrix can be produced by functions like SHSP (SHift to the South with Plane geometry). This summation appears to need three adds per point, but closer examination shows that intermediate results can be shared between nearby points, hence the use of the temporary matrix TEMP. In line 14, note again the multiplication of the scalar value 0.25 by every element of the matrix expression, and the masked assignment.

Line 15 evaluates the convergence criterion. Function ABS is applied element by element to its matrix argument. Then function MAXV returns a scalar result which is the maximum value of the elements in its matrix argument. This scalar value is then tested in the normal way inside the IF condition.

The above example illustrates how masked assignment is used for local conditional operations, whereas IF statements are used for global transfer of control, and hence tend to be used less frequently. Indeed, the manipulation of Boolean matrices and their use in masking, merging, and selection are important features of FORTRAN Plus.

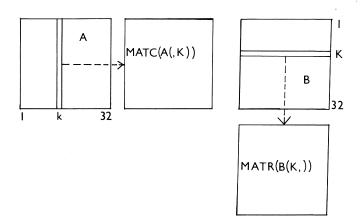

Replication of a scalar has been seen above, and it is also possible to replicate vectors. This involves an explicit call to a function, to specify how the vector is broadcast: MATR gives a matrix of identical rows, whereas MATC gives a matrix of identical columns. Various indexing constructs are also available: for example, the extraction of a specified row or column of a matrix giving a vector result.

FORTRAN Plus offers a range of precisions: integers from 8 bit to 64 bit wordlength, and reals from 24 bit to 64 bit wordlength, in steps of eight bits in each case. There is a continuous tradeoff between wordlength and performance, and of course memory usage.

# Assembly language

FORTRAN Plus provides a good match between the capabilities of the DAP hardware and the requirements of applications; the wordlength options and Boolean manipulation functions give great flexibility. However, in some applications areas other wordlengths or special number representations may be required for optimum performance.

These can be programmed in the assembly language

<sup>\*</sup> Previously known as DAP FORTRAN

# system description:

APAL. This necessarily involves bit level operations and detailed coding but two aspects mitigate the amount of work involved: the ability to mix FORTRAN Plus and APAL at the subroutine level, so it is often appropriate only to have a few critical routines in APAL; and the availability of powerful macro facilities in APAL, permitting in some cases an intermediate level language to be customized by the user.

# Run time system

DAP programs written in FORTRAN Plus or APAL (or both) are compiled on the host and downloaded into the DAP for execution. A standard host program (written in FORTRAN or C) controls the execution of the DAP program by calling routines that perform the following functions:

- Load a specified DAP object program into the DAP.

- Transfer a block of data in either direction between an area in the host program and a named COMMON block in the DAP program.

- Initiate DAP processing at a named subroutine within the DAP program. The host program is suspended while the DAP is running; when the DAP executes a RETURN from that top level subroutine, the DAP program halts, and the host program is restarted.

- Release the DAP resource; this is also of course done automatically when the host program terminates.

In the event of a program exception in the DAP, such as floating point overflow, the default action causes output of a pattern showing where in the array the errors occurred, together with a route map of the sequence of subroutine or function calls that led to the error. Interactive debugging, using names of variables as in the source code, is available, as well as tracing facilities.

A DAP simulation function provides all the above facilities, but running entirely on a serial processor. Naturally, any DAP-specific peripherals (such as the video display) are not modelled, and the performance is much lower than a real DAP, but this does provide a route for experimentation with short sections of DAP code.

# Library routines

The FORTRAN Plus compilation system incorporates extensive libraries of low level routines that implement arithmetic and data manipulation operations as the appropriate sequences of bit-level operations. The presence of such routines is however transparent to the user.

At a higher level, the extensive experience of using the DAP architecture has led to the provision of a wide variety of library routines to provide applications-related functions. Some example routines are:

- Matrix manipulation (e.g. inner product multiplication, inversion, eigenvalues)

- Signal processing (e.g. FFT and other transforms)

- Image processing (e.g. windowing, histograms, convolutions)

- Data reorganization (e.g. sorting, permutation)

- Functions (e.g. random numbers, transcendental functions)

- Graphics.

# Data mappings

The FORTRAN Plus programming example given earlier assumed a problem size that matched the PE array, or was smaller than the array. In practice, many problems are larger than the PE array, and in this case the processing is done in sections that match the size of the array.

The problem array is declared in FORTRAN Plus as a set of DAP-sized matrices, and the code works serially through the matrices of this set. The number of DAP-sized sections depends of course both on the problem size and on the size of DAP being used; the latter is accessible to the FORTRAN Plus program as a run-time value.

Two possible data mappings for 'oversize' problems are:

- Each array-sized section contains a neighbourhood of the problem array; this is referred to as a 'sheet' mapping.

- Each PE holds a neighbourhood of the problem array;

this is referred to as a 'crinkled' (or 'pyramidal')

mapping.

Which mapping is best depends on the pattern of communication between elements of the problem array. Often the best mapping is obvious, but in general the choice of mapping is an important aspect of algorithm design for processor arrays<sup>6</sup>.

The advanced user may wish to employ more sophisticated mappings, or to change mappings during the course of a computation. To assist with this, a scheme known as parallel data transforms (PDTs)<sup>7</sup> is available. This is both a compact notation for describing regular data mappings, and a means for automatically generating code to transform between different mappings. Some of the library routines, in particular FFTs and sorting, use these PDT techniques.

#### APPLICATION AREAS

DAP was created to tackle large computing problems such as the solution of field equations and matrix manipulation. It is indeed very successful at such tasks, but there is a growing awareness of its suitability for a wider class of problem, and alongside this an increasing repertoire of parallel techniques that can help with the conversion of seemingly serial processes to parallel form.

Successful DAP applications obviously use large regular data sets, but it is not necessarily the case that all the PEs are usefully active all the time. Indeed the

Table 1. Performance capability of DAP 610 for processing matrix operands

|        | Logical            | up to  | 40 000 | Mops   |

|--------|--------------------|--------|--------|--------|

| 8 bit  | Character          | up to  | 4 000  | Mops   |

| 8 bit  | Integer            | •      |        | -      |

|        | Add                |        | 1 600  | Mops   |

|        | Multiply           |        |        | Mops   |

|        | Multiply by scalar |        |        | P-     |

|        | constant           | 600 to | 1 200  | Mops   |

| 32 bit |                    | 000 10 | 1 200  | Wops   |

| 32 OIL | Add                |        | 48     | Mflops |

|        |                    |        |        |        |

|        | Multiply           |        | 32     | Mflops |

|        | Square             |        | 64     | Mflops |

|        | Divide             |        | 24     | Mflops |

|        | Square-root        |        |        | Mflops |

|        | Maximum value      |        |        | - F-   |

|        | (scalar result)    |        | 200    | Mflops |

|        | (Sealar result)    |        | 200    | ops    |

DAP, with its facilities for rapid manipulation of Boolean matrices and setting of activity patterns, often deals more effectively, in relative terms, with conditional operations than a serial processor.

The following list gives an indication of the scope of DAP applications areas; it is by no means exhaustive:

- Field equations: wind tunnel, wave equation, Navier– Stokes equation<sup>8</sup>, porous dam<sup>9</sup>

- Engineering: finite element analysis 10,11

- Linear algebra<sup>12</sup>

- Physics: Ising model<sup>13</sup>, molecular dynamics<sup>14</sup>, lattice gauge theory, galactic simulation<sup>15</sup>

- Medical: NMR image reconstruction, DNA sequence matching<sup>16</sup>

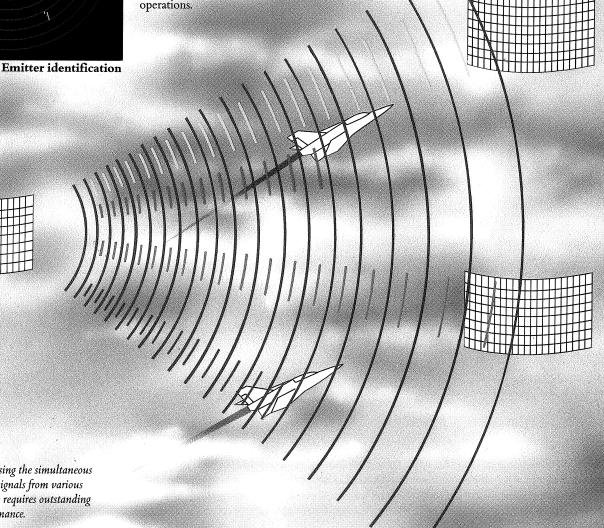

- Radar: signal processing<sup>4</sup>, shadow calculation

- Image manipulation<sup>17</sup>: filtering, feature extraction, rotation

- Graphics: molecular graphics<sup>18</sup>, ray tracing

- Character handling: data searching<sup>19</sup>, sorting

- Design automation: chip layout<sup>20</sup>, fault simulation.

# **PERFORMANCE**

Table 1 gives an indication of the performance capability of the DAP 610 (a DAP 600 running at 10 MHz) for processing matrix operands. The figures are given in units of Mflops (millions of floating point operations per second), or Mops (millions of operations per second).

Performance figures depend on the wordlength used, but also on the bit-level complexity of the function being performed, as illustrated by the figures above. For example, evaluating the element-by-element square of a matrix is faster than a general multiply because multiplication involves summation of a tableau of bits, and the library function exploits the symmetry in that tableau. Finding the maximum element of a matrix is fast because the algorithm uses an associative technique to progressively eliminate possibilities, starting by testing the most

significant bit position of the matrix; unlike the obvious serial version of this function, it never explicitly compares any elements of the operand matrix.

As already mentioned, Boolean operations are especially fast. The most favourable case is an operation between a value in a PE register plane and a value in a memory plane, and putting the result into a PE register. This takes just one clock cycle to produce one Boolean result in every PE, giving the enormous processing rate quoted in the table.

The DAP is generally much better able to achieve and sustain the quoted performance figures than a conventional processor, since operations such as address arithmetic and even data movement usually take much less time than computing the arithmetic results, whereas on a conventional processor the times for these 'overheads' are often comparable with, or even greater than, the arithmetic.

# **CONCLUSIONS**

The DAP has already shown its enormous potential, and its wide exposure to users has established a strong base of applications software and parallel algorithm techniques. The software is mature, permitting easy program development, and is ready to move forward with new developments in parallel processing languages. The recent emergence of DAP in a workstation environment makes it especially convenient to use, and the inbuilt display capability gives new insights into the nature of the computations as they are being performed.

#### REFERENCES

- 1 Parkinson, D, Hunt, D J and MacQueen, K S 'The AMT DAP 500' Proc. 33rd IEEE Comp. Soc. Int. Conf. (February 1988)

- 2 Flanders, P M, Hunt, D J, Reddaway, S F and Parkinson, D 'Efficient high speed computing with the distributed array processor' in Kuck, D J, Lawrie, D H and Sameh, A H (Eds) High speed computer and algorithm organisation Academic Press, USA (1977)

- 3 Hunt, D J and Reddaway, S F 'Distributed processing power in memory' in Scarrott, G G (Ed) The fifth generation Pergamon-Infotech, UK (1983)

- 4 Reddaway, S F, Roberts, J B G, Simpson, P and Merrifield, B C 'Distributed array processors for military applications' MILCOMP 85. Military computers, graphics and software Microwave Exhibitions and Publishers Ltd, Tunbridge Wells, UK (1985) pp 74-82

- 5 Gostick, R W 'Software and algorithms for the distributed array processors' *ICL Tech. J.* (May 1979) pp 116–135

# system description:

- 6 Flanders, P M 'Non-numerical methods on parallel computers' Comp. Phys. Commun. Vol 26 (1982) pp 363-371

- 7 Flanders, P M 'A unified approach to a class of data movements on an array processor' *IEEE Trans.* Comput. Vol C-31 No 9 (September 1982)

- 8 Grosch, C E 'Adapting a Navier-Stokes code to the ICL DAP' SIAM J. Sci. Stat. Comput. Vol 8 No 1 (1987)

- 9 Cryer, C W, Flanders, P M, Hunt, D J, Reddaway, S F and Stansbury, J 'The solution of linear complementarity problems on an array processor' J. Comp. Physics Vol 47 No 2 (August 1982)

- 10 **Ducksbury, P G** Parallel array processing Ellis Horwood Ltd, UK (1986)

- 11 Lai, C H and Liddell, H M 'A review of parallel finite element methods on the DAP' Appl. Math. Modelling (11 Oct 1987) pp 330-340

- 12 Reddaway, S F, Bowgen, G and van den Berghe, S 'High performance linear algebra on the AMT DAP 510' Proc. SIAM Conf. Parallel Processing for Scientific Computing (December 1987)

- 13 Reddaway, S F, Scott, D M and Smith, K A 'A very high speed Monte Carlo simulation on DAP' Comp. Phys. Commun. Vol 37 (1985) pp 351-356

- 14 Bowler, K C and Pawley, G S 'Molecular dynamics and Monte Carlo simulations in solid state and

- elementary particle physics' *Proc. IEEE* Vol 72 No 1 (1984) pp 42-55

- Johns, T C and Nelson, A H 'Particle simulation of 3D galactic hydrodynamics on the ICL DAP' Comp. Phys. Commun. Vol 37 (1985) pp 329-336

- 16 Lyall, A, Hill, C, Collins, J F and Coulson, A F W 'Implementation of inexact string matching algorithms on the ICL DAP' in Feilmeir, M, Joubert, G R and Schendel, U (Eds) Proc. Conf. Parallel Computing 83 North-Holland, Amsterdam (1984)

- 17 Oldfield, D E and Reddaway, S F 'An image understanding performance study on the ICL distributed array processor' IEEE Comp. Soc. Workshop Computer Architecture for Pattern Analysis and Image Database Management (November 1985)

- 18 Hubbard, R E and Fincham, D 'Shaded molecular surface graphics on a highly parallel computer' J. Mol. Graphics Vol 3 No 1 (March 1985)

- 19 Reddaway, S F and Page, R M R 'High speed data searching with a processor array' in Winter, S and Schumny, H (Eds) Proc. Conf. Euromicro 88, Zurich Elsevier Science Publishers, UK (1988)

- 20 Hunt, D J 'Tracking of LSI chips and printed circuit boards using the ICL distributed array processor' in Feilmeir, M, Joubert, G R and Schendel, U (Eds) Proc. Conf. Parallel Computing 83 North-Holland, Amsterdam (1984)

Active Memory Technology Ltd 65 Suttons Park Avenue Reading Berks RG6 1AZ United Kingdom Tele. 0734 661111 Active Memory Technology Inc. 16802 Aston Street Suite 103 Irvine CA 92714 USA

Tele. (714) 261 8901

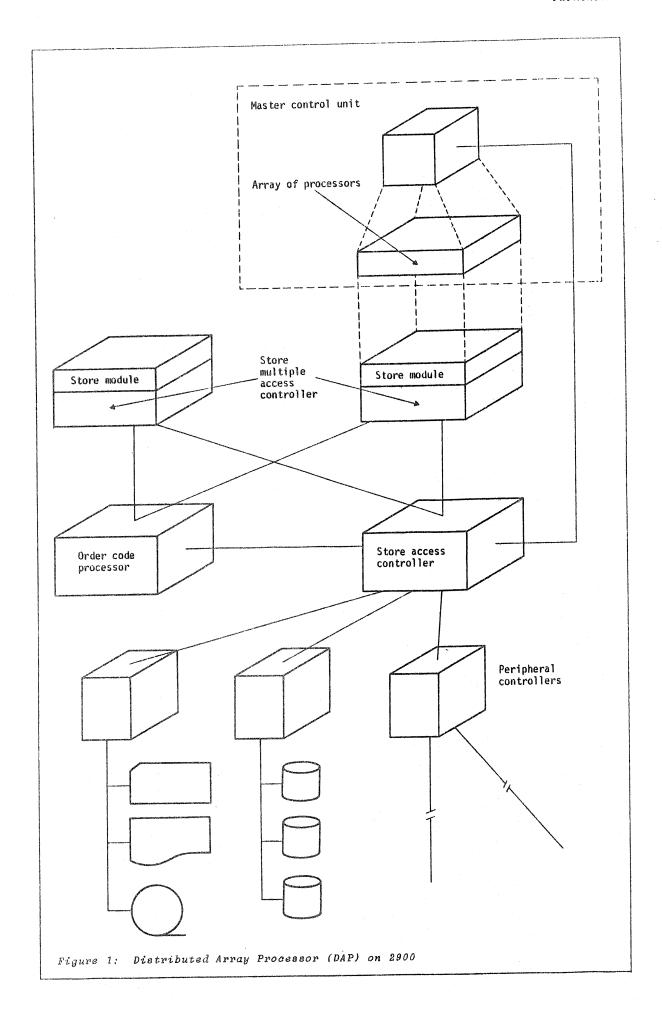

THE ICL DISTRIBUTED ARRAY PROCESSOR

D Parkinson

Large Systems National Research Region International Computers Limited London

<sup>©</sup> D Parkinson 1977

D PARKINSON is a graduate of Queen's University Belfast having taken a 1st Class

Honours Degree in Applied Mathematics and a PhD in Theoretical Quantum Physics. He

has worked on the use of large computers to solve large-scale numerical problems for

both the United Kingdom Atomic Energy Authority at Aldermaston, England, and the European Space Research Organization (now ESA) in Rome. In 1973 he joined ICL as a consultant in scientific programming and has recently been mostly concerned with the development of the ICL Distributed Array Processor.

THE ICL DISTRIBUTED ARRAY PROCESSOR

#### INTRODUCTION

Once upon a time goods were manufactured by a single craftsman who chose and purchased the materials, made his product and then sold the results of his own labours in his own shop.

The requirement for high volume, low cost production has led to the development of manufacturing industries using many people of lower skill levels who all cooperate to produce the finished product. In many ways computing and computers are still in the era of the single highly skilled craftsman. Most modern computers consist of a single central processing unit which accepts data and programs from peripherals, performs a number of manipulations upon it and sends the results to other peripherals. The major trend in computer improvement over the years has kept to this basic concept with only minor changes, allowing some power to peripheral processors to off-load some of the simpler tasks (making the apprentices serve in the shop). Computer power has increased mainly by increasing the skill level of the central processor (floating-point hardware, pipelining, etc).

The increasing demands for more and more computing with high cost-effectiveness is, however, leading to some unconventional computer designs which are no longer just more skilful versions of the von Neumann machine. New computer designs are appearing which replace the single processor with squads of processors. Although each individual processor in the squad may not be as powerful as the most powerful single processors the combination is much more powerful and cost-effective.